先进半导体的工艺会给芯片成本带来多少变化?

摘要: 先进工艺制程成本的变化是一个有些争议的问题。成本问题是一个复杂的问题,有许多因素会影响半导体制程成本。本文将讨论关于半导体制程的种种因素以及预期。晶圆成本影响半导体工艺制程成本的第一个因素是晶圆成本。

先进工艺制程成本的变化是一个有些争议的问题。成本问题是一个复杂的问题,有许多因素会影响半导体制程成本。本文将讨论关于半导体制程的种种因素以及预期。

晶圆成本

影响半导体工艺制程成本的第一个因素是晶圆成本。

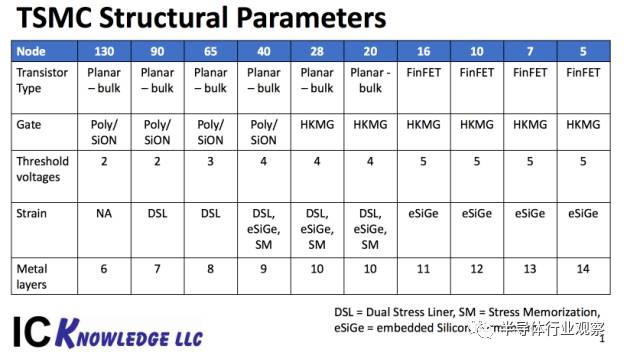

毫无疑问,晶圆成本在不断上升。制程的金属层数随着工艺的演进不断上升,在130nm时典型的制程有六层金属,而到了5nm节点则预期至少会有14层金属。

从90nm节点开始开始引入应力技术以继续增强晶体管的性能,这也会增加制程的成本。从45nm到28nm节点,半导体制程引入了high-k栅技术以增强性能。

另一个变化是晶体管阈值电压数目的变化。在130nm节点,晶体管只有两种阈值(常规阈值RVT管与低阈值LVT管),而到了16nm之后,有了多达五种阈值(超高阈值UHVT,高阈值HVT,常规阈值RVT,低阈值LVT与超低阈值ULVT)。这是因为,从40nm到16/14nm FinFET,短沟道效应越来越明显,为了控制漏电流必须引入多种阈值的器件。显然,这也会增加掩膜成本。

在先进半导体制程中,还会引入新的技术,如在16/14nm节点引入的FinFET技术,在5nm引入的堆叠横向纳米线(stacked horizontal nanowire )技术。

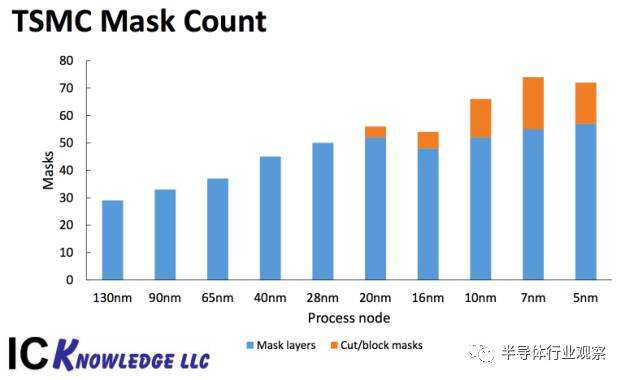

上图显示了不同工艺节点用到的技术,据此不同的工艺节点用到的掩膜层数如下图所示:

新的光刻技术

从20nm节点开始,为了使用传统光刻技术实现更小的特征尺寸,半导体制程引入了多重pattern技术。光刻机在28nm的时候只需要一次的光刻曝光就可以实现了。

但到了22nm/20nm,单次曝光有时候就不能给临界层提供足够的分辨率。芯片制造商就通过多重pattern的方式解决问题。这也就是增加了一个简单的两步流程。这当中的主要的挑战就是刻这些细线图案。

为了达到目标,芯片制造商只好使用双重pattern技术。在这个步骤里会需要两次光刻和刻蚀步骤去确定一个单层。使用这种双重pattern技术,可以减小30%的pitch,而三重pattern则需要三次曝光,也就是需要三次刻蚀步骤。

除此之外,业界在10nm和7nm还会碰到其他问题。在45nm和40nm的时候,设计的时候需要用到40层光罩,而到了14nm和10nm,光罩的需求量则上升到60层。“如果没有EUV,只是靠沉浸式去实现三倍甚至四倍pattern,那么我们认为在7nm的时候,光罩数量会上升到80到85层之间”。三星的晶圆制造资深主管Kelvin Low表示。

光罩层数的增加,也就代表着成本的水涨船高。同时覆盖物也将会成为Fab的灾难。覆盖物需要把光罩层有秩序的精确地放置在彼此的身上。而随着mask的增加,覆盖层也就会成为噩梦。如果没对齐,覆盖层问题就够你喝一壶了。

另外,现在做一层光罩需要1到1.5天,在7nm的时候使用多重pattern,那就需要差不多五个月的时间才能做好晶圆。这就意味着如果继续使用多重pattern,会导致晶圆成本高到无法接受。

除了多重pattern之外,另一种新的光刻技术是EUV。然而,EUV的掩膜制造也十分困难。EUV掩膜在很多方面与传统193nm光刻的掩膜不一样。因为它有很大的改变,对于每个产品的特性或者功能,在供应链中会产生很大影响,其中包括光刻胶、掩膜及中间掩膜,也涉及制造设备,如采用电子束写入设备以及软件。

在5纳米时,掩膜的写入时间是最大的挑战。因为今天的单电子束写入设备在做复杂图形时的出货不够快,费时太久。从己经出炉的报告来看,由于技术原因,设备的研发用了比预期长得多的时间。事实上,任何突破性的创新技术从研发到成功,再达到量产水平,都是如此。

另外,即使使用EUV,多重pattern也是必须的。只有在真正的关键层才需要采用EUV,而其他层仍然用多重pattern。可以说,在未来这样的混合模式光刻是趋势。

而且,当EUV延伸至7纳米以下时,作为一种提高光刻机放大倍率的方法,需要大数值孔径的镜头(NA),为此ASML已经开发了一种变形镜头。它的两轴EUV镜头在扫描模式下能支持8倍放大,而在其他模式下也有4倍,因此NA要达0.5至0.6。

由此带来的问题是EUV光刻机的吞吐量矛盾,它的曝光硅片仅为全场尺寸的一半,与今天EUV光刻机能进行全场尺寸的曝光不一样。最新 EUV 机器的价格超过 1 亿欧元,是现有常规 193nm 光刻机价格的二倍多。

数字门密度与数字门成本

特征尺寸缩小最大的动力就是大规模ASIC中数字门尺寸缩小,从而在相同的芯片面积上可以放下更多的性能更好的标准单元。最终ASIC的成本应当同时考虑晶圆的成本以及门单元的密度。

数字门单元的尺寸在横向上决定于多晶硅以及多晶硅通孔的间距,而在纵向上则等于金属间最小间距乘以track数目。Track数越小,门尺寸越小,但是布线也越困难。

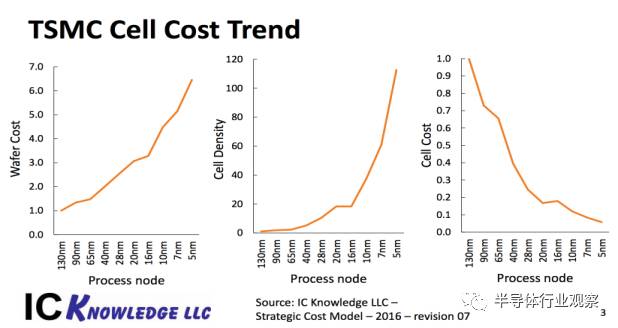

晶圆成本,数字门密度与数字门成本如下图左所示。在130nm到65nm之间,晶圆成本上升的速度较慢,此后在40nm到20nm之间,晶圆成本上升由于加入了更多阈值电压的晶体管而加快上升。在20nm之后,晶圆成本上升速度再次加快,这次是因为多重pattern。

数字门密度如下图中所示,密度以指数趋势上升,该趋势与摩尔定律相符。单位数字门成本如下图右所示,可见从130nm到20nm节点之间单位门成本下降较快,但是20nm之后单位门成本下降速度减缓。

Dark Silicon

目前芯片设计都有严格的功耗指标。随着门单元密度随指数上升,单位面积的功率密度也随指数上升,但是芯片散热能力上升却没这么快。为了解决散热问题,在芯片上出现了Dark Silicon,即芯片上部分晶体管在大多数时候是不上电的,仅仅在用到的时候才会启动。

这些Dark Silicon面积包括各类加速器,举例来说手机SoC里面的视频编解码模块的电源在不播放视频的时候是关掉的。这些Dark Silicon在大部分时间是不起作用的,从另一个角度说Dark Silicon也增加了芯片的成本。

设计成本

在先进工艺设计成本可谓是一飞冲天。这就导致了在先进工艺下,芯片出货量需要非常大才能抵消NRE成本。如今,越来越少的设计可以满足如此大的出货量,因此很多设计出于经济上的考量不再使用最先进的工艺。

结语

尽管先进工艺的晶圆成本不断攀升,门单元的成本却能够保持下降。然而,过高的设计成本却成了一个问题,只有出货量非常大的芯片才有机会使用最新工艺。

nm,成本,技术,光刻,上升